検出不可能なものを検出する

半導体の3D構造には、検出が困難な埋没欠陥が含まれることがあり、その結果、低レベルのリークやばらつきが生じ、相互接続抵抗やトランジスタの性能に大きなばらつきが生じ、設計サイクル時間が数カ月も余分にかかることになります。

しかし、PDFソリューションズのDesign-for-Inspection™を使用すれば、「Middle of Line」インライン検査でこれらの問題を発見し、市場投入までの時間を最大4~6ヶ月短縮することができます。

DOWNLOAD the DFI datasheet

検査のためのデザイン」とは何か?

当社のDesign-for-Inspection System(DFI™システム)は、3D構造内部に埋もれた電気的関連欠陥を1時間当たり数億個のDUTで検出できる非接触型電子ビーム測定システムです。半導体製造の中間工程でインラインで使用できるほど高速です。

潜在的な信頼性リスクの早期把握

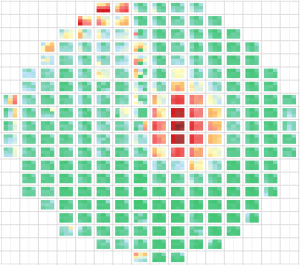

DFIシステムは、ウェハあたり数十億の構造を効率的にスキャンして、PPMからPPBレベルの微小なリークを特定し、ダイの潜在的な弱点に関する独自の信頼性洞察を提供します。このシステムは、単一故障タイプについてはすべてのダイの高解像度マップを、すべての故障タイプについては複合マップを提供します。この詳細なダイ横断測定は、GDBN(Good Die Bad Neighborhood)のような総体的手法よりも、先見の明を提供し、ダイごとに優れたリスク・スクリーニングを可能にします。

製造実証済み

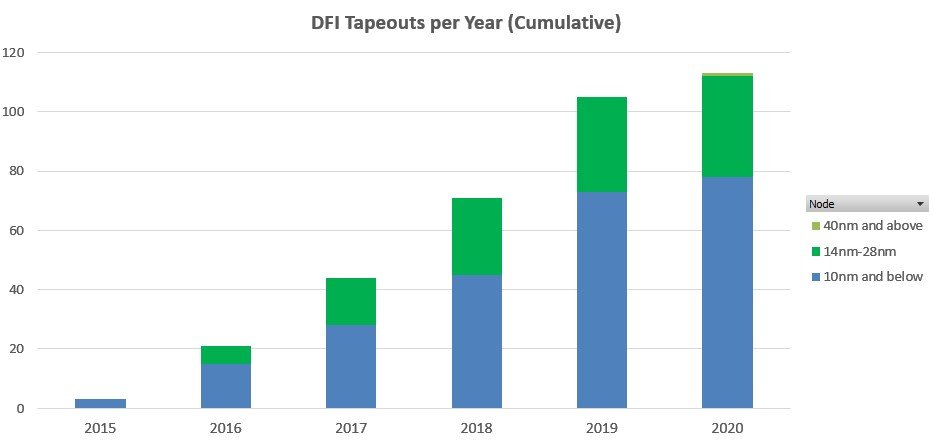

当社のDFIシステムは、28nmから5nmまでの7つの先端プロセスノードにまたがり、現在までに120以上のテープアウトで実現されています。さらに、60台以上のPDF Characterization VehicleがDFIコンテンツでテープアウトされています。

DFIシステムの仕組み

DFIシステムは、設計に挿入される特許取得済みのIPセルと、それらのIPセルの電気的応答を読み取る特殊で高性能な電子ビーム・ハードウェアの組み合わせです。これらを組み合わせることで、歩留まり、性能、信頼性を制限するプロセスやレイアウトのセンシティビティを特定し、通常は数カ月後にならないと見たり測定したりできず、コストのかかる設計のやり直しや市場投入時期の遅れにつながる設計上の問題を予見することができます。

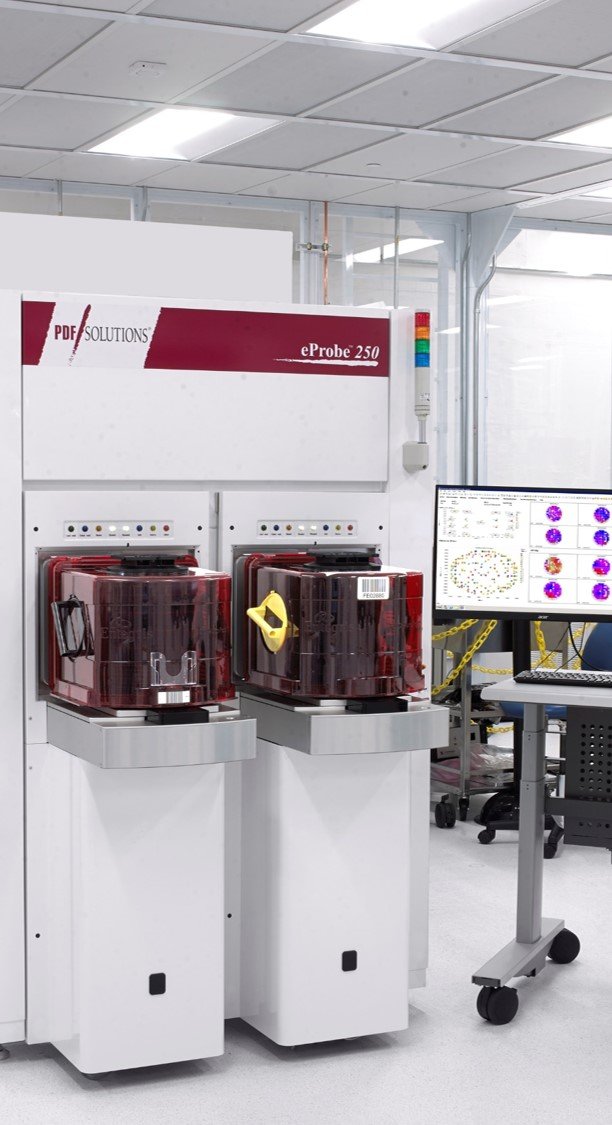

高性能、インラインEビーム検査

当社の特許取得済みIPセルは、当社の非接触e-beamテスト測定システムeProbe® 150および250により、製造ラインの中間工程で読み取られます。これらのシステムは現在、世界中の複数の拠点に配備されており、複数のノード(22nm、14nm、7nm、5nm)での歩留まり学習に積極的に使用されている。eProbe 250のスループット性能は、1時間当たり1億DUTをはるかに超え、インライン検査に十分な速度です。